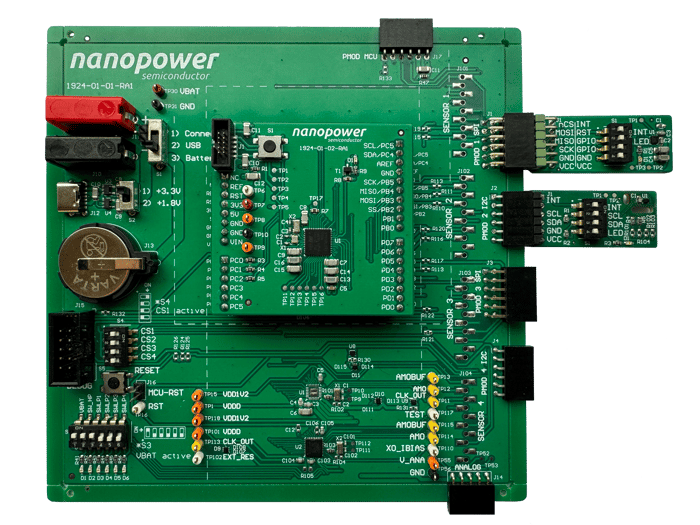

nPZero DevKit - NPDK-CK-G1SY

$99.00nPZero G1SY DevKit

Offers up to 90% reduction in power consumption

consumption

reduction

View and download the datasheet for the nPZero power-saving IC.

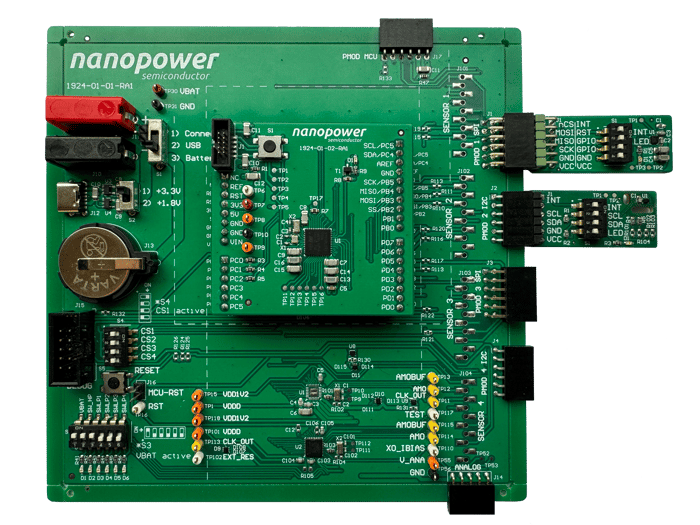

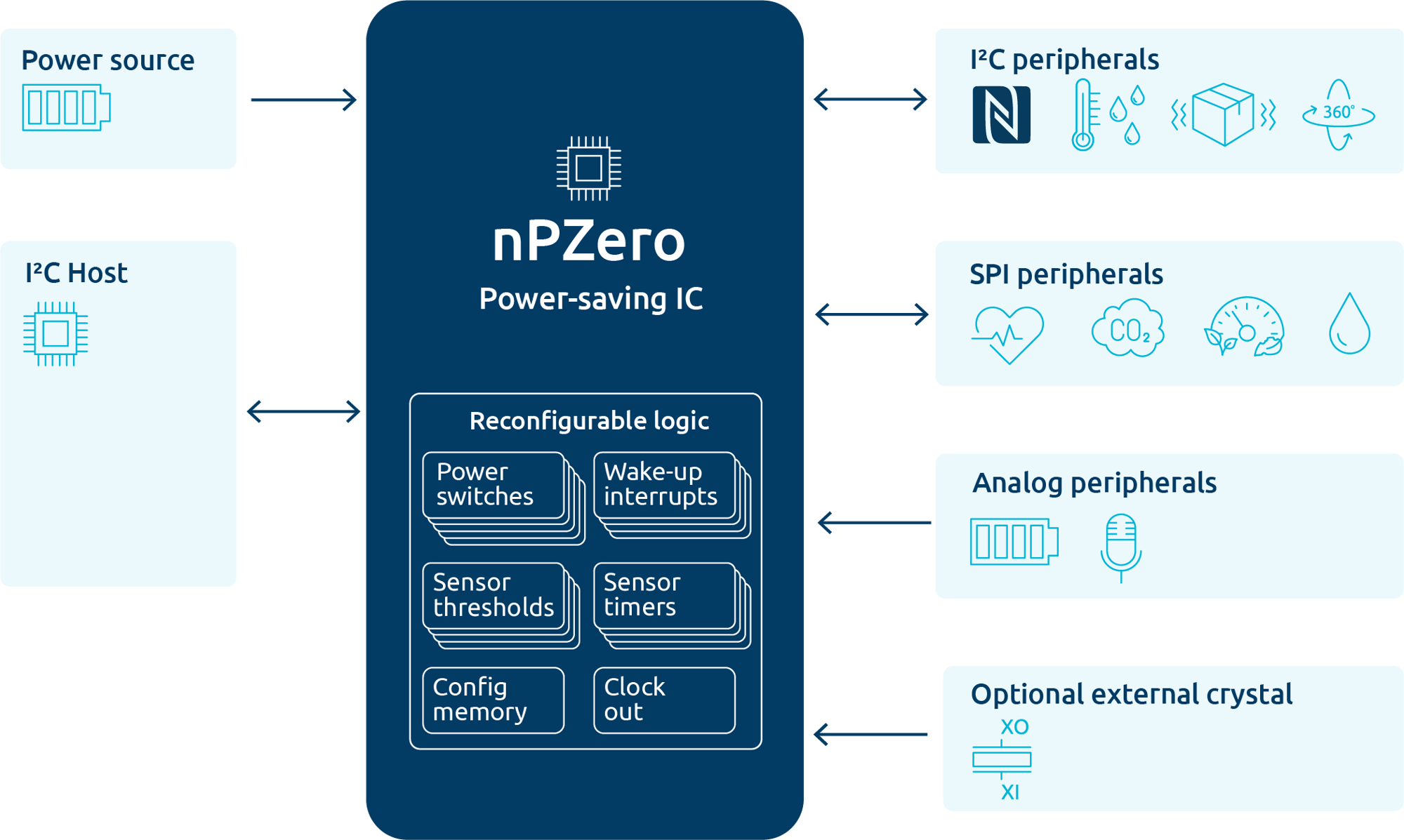

The nPZero power-saving IC with the nPZero architecture redefines low power.

The nPZero architecture represents a fundamentally new approach to designing battery-constrained systems. An active system without an active microcontroller is now a possibility:

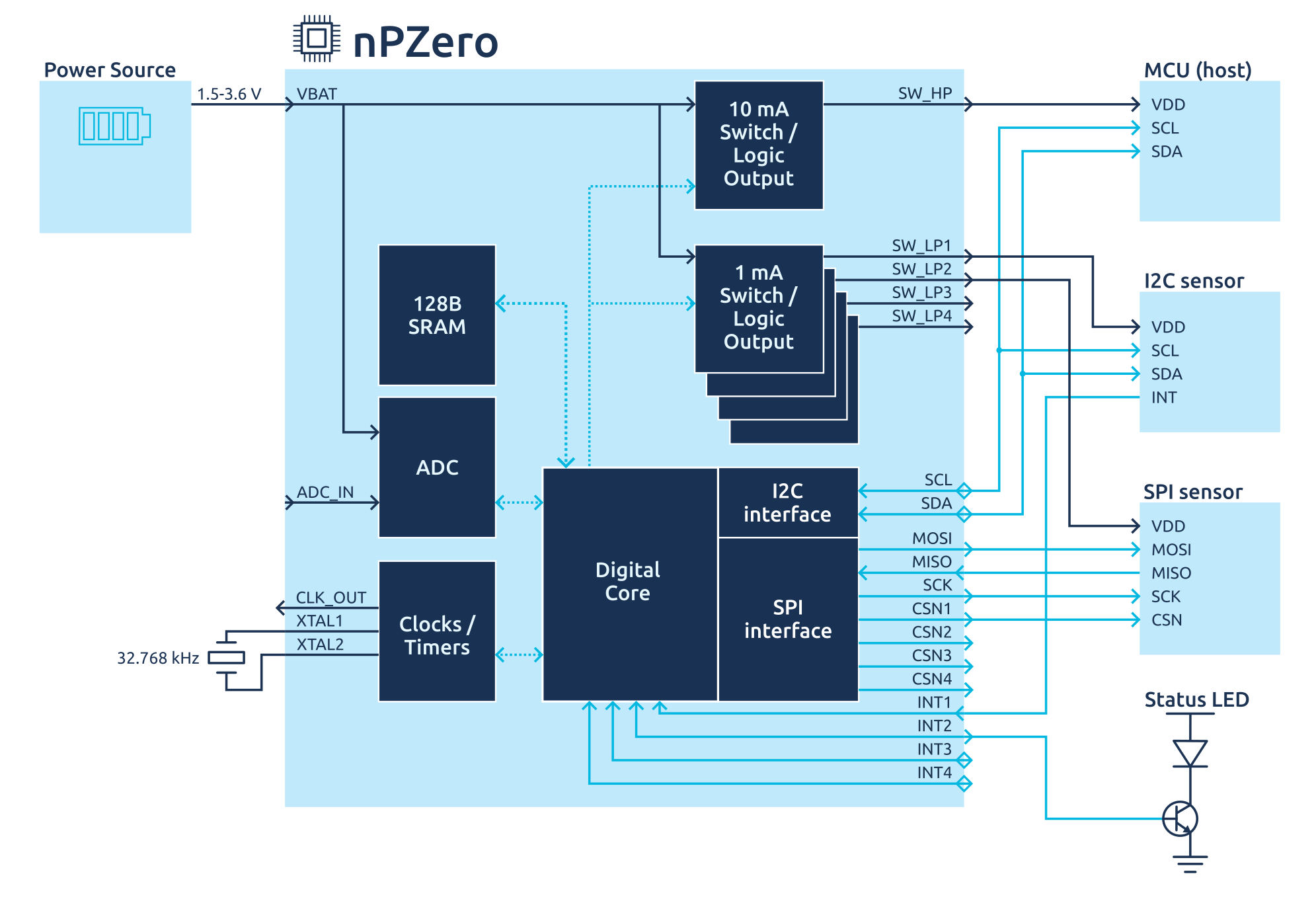

The nPZero power-saving IC can operate the entire system without an active host, e.g., MCU, processor, or wireless SoC. It can take over the controller role and manage peripherals like sensors, and later hand the controller role back to the host based on user-configurable rules. This enables the power-hungry host to be shut down while keeping functions and responsiveness intact. As a true power manager, the peripherals’ power consumption is also optimized.

What differentiates the nPZero power-saving IC from other products on the market:

consumption through a full subthreshold design.

with a range of peripherals (I2C and SPI) and hosts (MCU, processor, or wireless SoC).

enables the host to be powered off while the system is still operating. Peripherals are managed without an active host. The nPZero IC takes over the controller role in the system; powering up, configuring, and reading peripherals. When required, the controller role is handed back to the host.

with the ability to act dependent on user-defined rules. A programmable logic with a reconfigurable state machine that enables actions based on events. For example, sensor values above/below a set threshold can trigger actions, including, e.g., waking up the host to initiate wireless communication.

by individual power cycling of peripherals to ensure the lowest possible power consumption.

to store commands, peripheral and host configurations, and sensor values.

with different alternatives depending on accuracy requirements.

for specific applications with API for programming via the host.

Units are limited. First come, first served